# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Roddy Alexander Romero Antayhua

# AMPLIFICADOR DE GANHO VARIÁVEL CONTROLADO POR RAZÃO CÍCLICA

Florianópolis

2012

## UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Roddy Alexander Romero Antayhua

## AMPLIFICADOR DE GANHO VARIÁVEL CONTROLADO POR RAZÃO CÍCLICA

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do grau de Mestre em Engenharia Elétrica. Orientador: Prof. Dr.,

UFSC Prof.Fernando Rangel de Sousa

Florianópolis

2012

#### Roddy Alexander Romero Antayhua

### AMPLIFICADOR DE GANHO VARIÁVEL CONTROLADO POR RAZÃO CÍCLICA

Esta Dissertação foi julgada adequada para obtenção do Título de Mestre em Engenharia Elétrica e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina. Florianópolis, 19/10/2012.

Prof. Patrick Kuo Peng, Dr., UFSC

# Coordenador do Curso Banca Examinadora: Prof.Fernando Rangel de Sousa, Dr., UFSC Orientador Prof. Raimes Moraes, Ph.D., UFSC Eng. Murilo Pessatti, M.Sc., Chipus Prof.Jefferson Luiz Brum Marques, Ph.D., UFSC Prof. Jader Alves De Lima Filho, Dr., UFSC

| A mis padres, porque a ellos les debo todo.<br>(Aos meus pais, porque eu devo tudo a eles). |  |

|---------------------------------------------------------------------------------------------|--|

|                                                                                             |  |

|                                                                                             |  |

|                                                                                             |  |

|                                                                                             |  |

|                                                                                             |  |

#### RESUMO

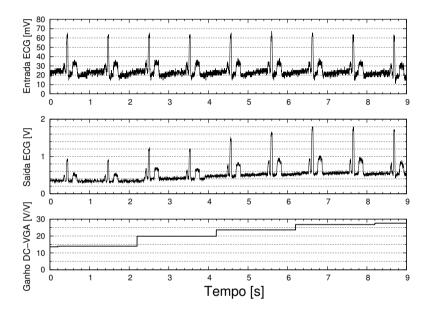

Um amplificador de ganho variável (VGA) ajustado digitalmente pela razão cíclica do sinal de controle é apresentado neste trabalho. O circuito baseia-se no princípio superregenerativo criado por Armstrong na década de 1920. Através desta técnica, consegue-se obter um ajuste fino do ganho sem necessidade de utilizar um DAC como interface entre o controle digital e o amplificador, como visto nos VGAs convencionais. O projeto foi contextualizado dentro de um sistema de aquisição de sinais biopotenciais e foi realizado em um processo de fabricação de 0,18 µm CMOS padrão. Os resultados, a partir de simulações, mostraram que o projeto cumpre com as especificações, atingindo, entre outras características, uma faixa de ganho de 45 dB com uma banda de 1,25 kHz, um consumo de 6.4 µW e uma faixa linear de 900 mV para uma THD de 0,5%. Algumas medições preliminares foram feitas as quais comprovaram o funcionamento do circuito. Em complemento ao VGA integrado, uma versão com componentes discretos foi implementada com o intuito de verificar a sua funcionalidade numa aplicação real. O circuito final incluiu um estágio analógico de entrada completo, o qual foi voltado para a medição de sinais cardíacos utilizando apenas dois eletrodos. Os resultados do protótipo discreto validaram o princípio de amplificação proposto no VGA para este tipo de aplicação.

**Palavras-chave**: Amplificador de ganho variável, razão cíclica, projeto de sinal misto, estágio analógico de entrada, biopotenciais.

#### **ABSTRACT**

In this work, a variable-gain amplifier (VGA) adjusted by the dutycycle of a control signal is presented. This circuit is based on the superregenerative concept created by Armstrong back in the 1920's. The chosen technique allows to perform a fine control of the gain without any DAC at the interface between the digital control and the amplifier, as usually seen in other VGAs. A 0.18 µm standard CMOS process was used for the design. Specifications were satisfied by simulation results, in which, among other results, it was obtained a gain range of 45 dB within a 1.25 kHz bandwidth, a power consumption of  $6.4 \mu W$  and 900 mV of linear range for a 0.5 % THD. Some preliminary measurements of the chip proved also the correct functioning of the circuit. As a complement of the integrated VGA, a discrete-component version was also implemented in order to verify its functionality in a real application. The final circuit included a complete analog front-end which was optimize for cardiac signals measurement using only two electrodes. The results of the discrete-component prototype validated the amplification principle proposed in the VGA for this type of aplication.

**Keywords**: Variable gain amplifier, duty-cycle, mixed-signal design, analog front-end, biopotentials.

# LISTA DE FIGURAS

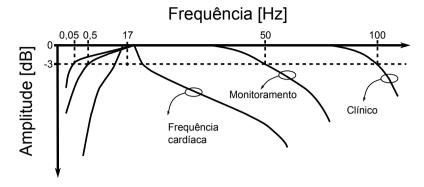

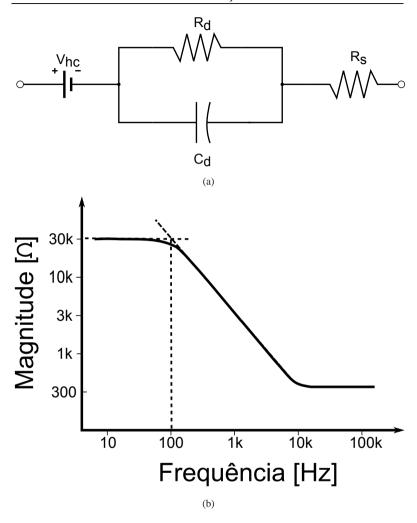

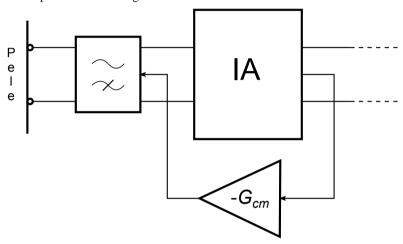

| 1  | processamento de sinais                                                                                                                                                                                                                                                                                             | 27 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

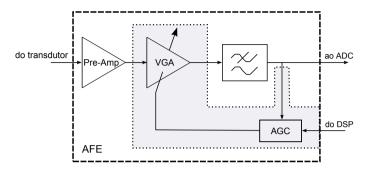

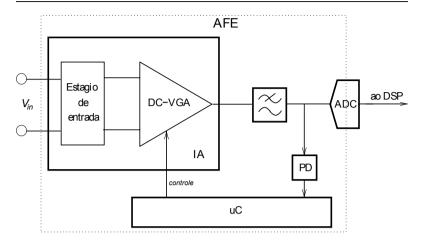

| 2  | Diagrama de blocos de um estágio analógico de entrada (AFE) típico                                                                                                                                                                                                                                                  | 28 |

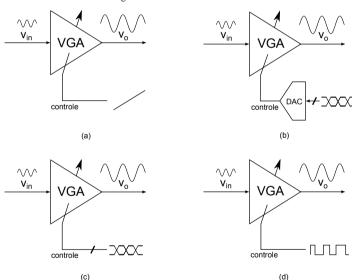

| 3  | Classificação dos VGAs segundo o seu tipo de sinal de controle: VGA com controle analógico (a), VGA com controle analógico e DAC de interface (b), PGA (c) e VGA com controle por razão cíclica (d).                                                                                                                | 30 |

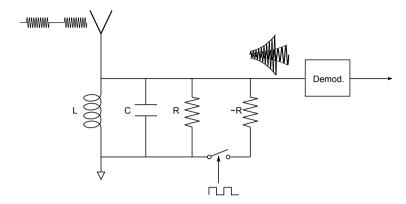

| 4  | Conceito do receptor superregenerativo, adaptado de [19]                                                                                                                                                                                                                                                            | 36 |

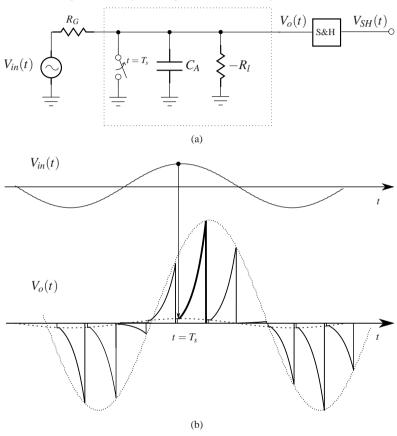

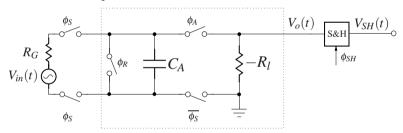

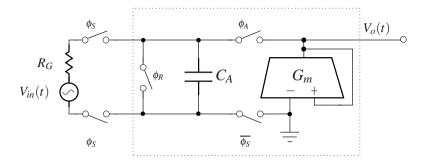

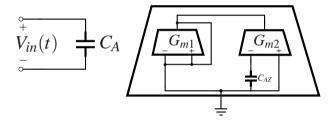

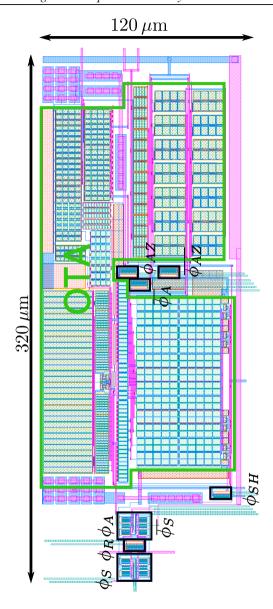

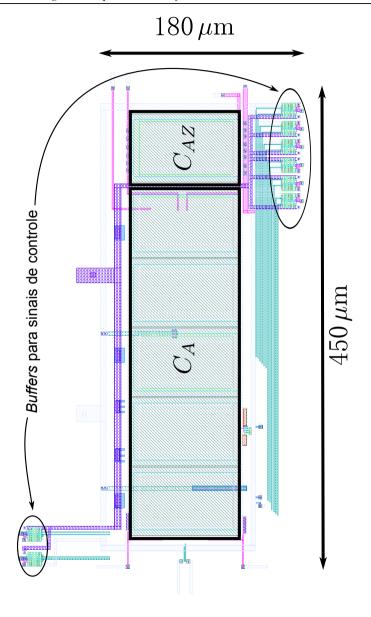

| 6  | Diagrama esquemático conceitual do amplificador proposto.                                                                                                                                                                                                                                                           | 39 |

| 7  | Fases de funcionamento do amplificador proposto                                                                                                                                                                                                                                                                     | 40 |

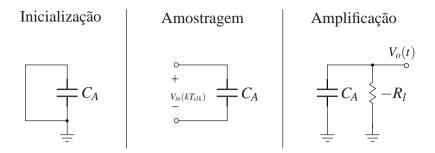

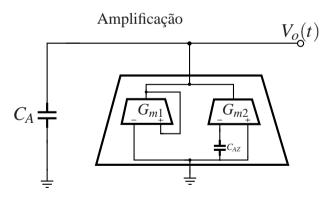

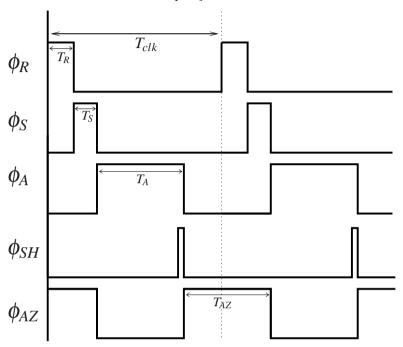

| 8  | Diagrama de tempos do amplificador proposto, onde podem ser observados os sinais de controle das fases de inicialização $(\phi_R)$ , amostragem $(\phi_S)$ , amplificação $(\phi_A)$ e amostragem e retenção $(\phi_{SH})$ , assim como o ciclo total de operação $(T_{clk})$ e o intervalo de amplificação $(T_A)$ | 41 |

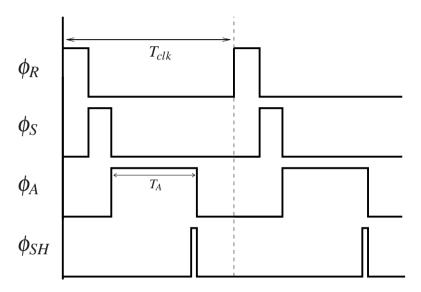

| 9  | Circuito para calcular a resistência equivalente de um OTA em realimentação positiva                                                                                                                                                                                                                                | 43 |

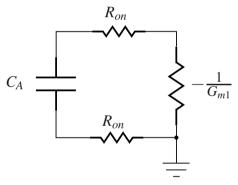

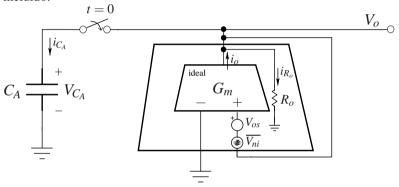

| 10 | Representação do DC-VGA com a resistência negativa implementada com um OTA em realimentação positiva                                                                                                                                                                                                                | 44 |

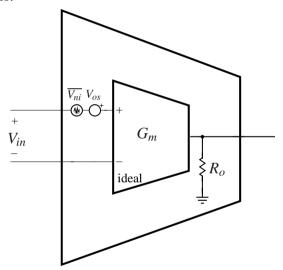

| 11 | Modelo do OTA representando as suas não-idealidades: impedância de saída em frequências baixas ( $R_o$ ), tensão de <i>offset</i> referida à entrada $V_{os}$ e ruído referido à entrada $(\overline{V_{ni}})$ .                                                                                                    | 45 |

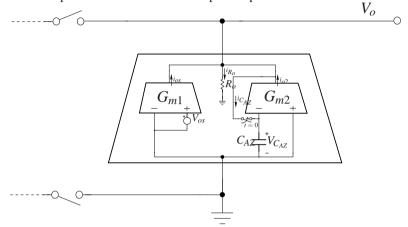

| 12 | Representação do DC-VGA incluindo a técnica de <i>Auto- Zero</i>                                                                                                                                                                                                                                                    | 47 |

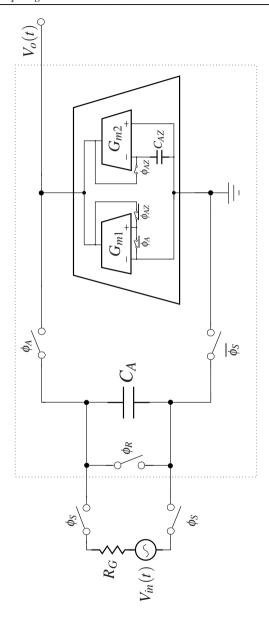

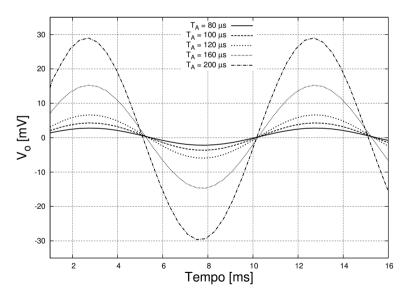

| 13  | Funcionamento do DC-VGA por fases incluindo o processo de <i>Auto-Zero</i> . Podem ser observados os sinais                            |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

|     | de controle das fases de inicialização ( $\phi_R$ ), amostragem                                                                        |    |

|     | $(\phi_S)$ , amplificação $(\phi_A)$ , amostragem e retenção $(\phi_{SH})$ e                                                           |    |

|     | $Auto-Zero$ ( $\phi_{AZ}$ ), assim como o ciclo total de operação                                                                      |    |

|     | $(T_{clk})$ e os intervalos de inicialização $(T_R)$ , amostragem                                                                      |    |

|     | $(T_S)$ , amplificação $(T_A)$ , e <i>Auto-Zero</i> $(T_{AZ})$                                                                         | 48 |

| 14  | Diagrama de tempos dos sinais de controle para o DC-VGA incluindo o processo de <i>Auto-Zero</i>                                       | 49 |

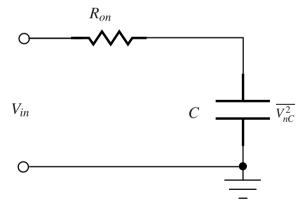

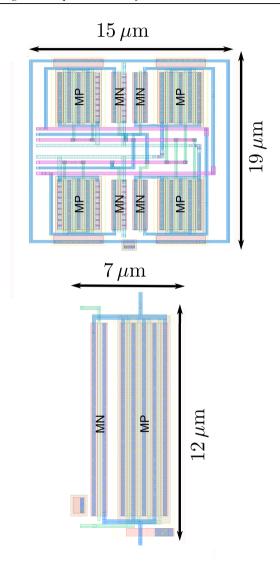

| 15  | Representação de um circuito de S&H para sua análise de                                                                                |    |

|     | ruído                                                                                                                                  | 51 |

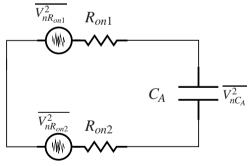

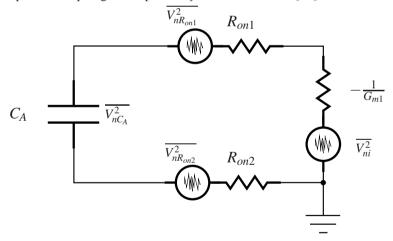

| 16  | 1                                                                                                                                      | 52 |

| 17  | Circuito para analisar o ruído na amplificação.                                                                                        | 53 |

| 18  | Representação da faixa de frequências válidas para a                                                                                   |    |

|     | operação do DC-VGA: Frequência de operação $(F_{clk})$ ,                                                                               |    |

|     | frequência mínima de operação ( $f_{min}$ ), frequência máxima de operação ( $f_{max}$ ), frequência de canto do ruído <i>flicker</i>  |    |

|     | do OTA $(f_{c1})$ e frequência máxima do sinal de entrada $(f_h)$ .                                                                    | 55 |

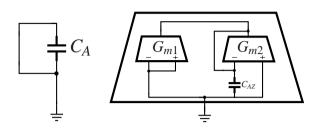

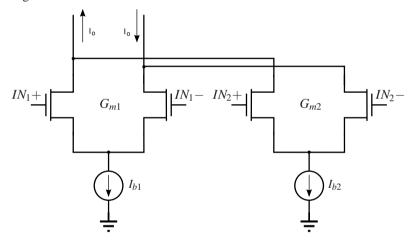

| 19  | Representação do OTA de duas entradas adequado para a                                                                                  | 33 |

| 1)  | técnica de <i>Auto-Zero</i> (adaptado de [24])                                                                                         | 58 |

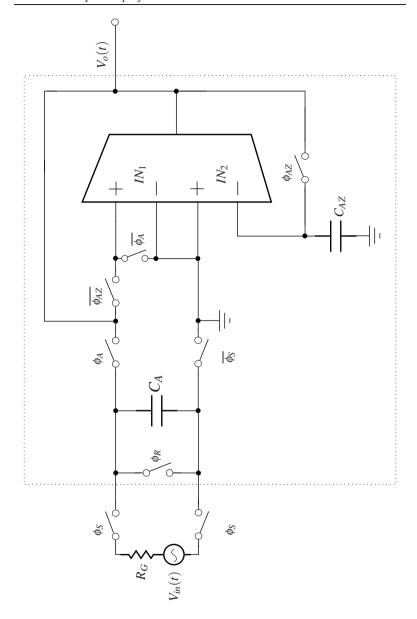

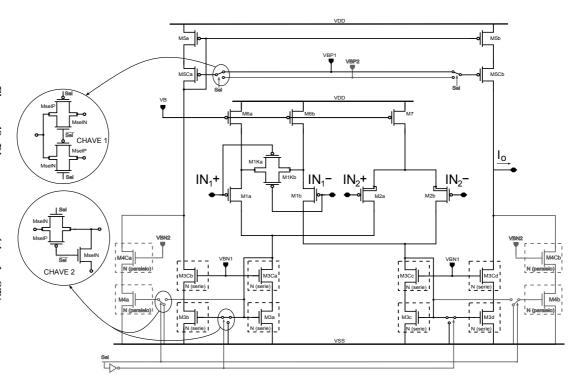

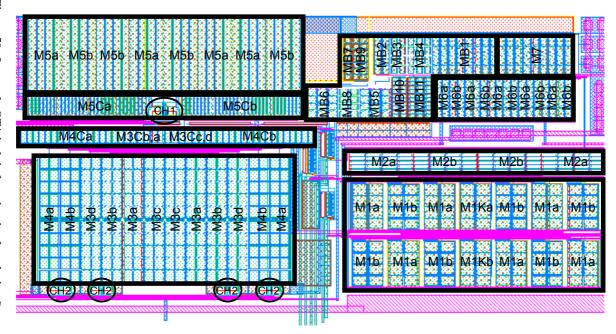

| 20  | Diagrama esquemático do circuito final do DC-VGA                                                                                       |    |

|     | baseado na implementação do OTA de dupla entrada                                                                                       |    |

|     | proposta em [24]                                                                                                                       | 59 |

| 21  | O efeito do $R_{on}$ das chaves na constante de tempo $(\tau)$                                                                         | 61 |

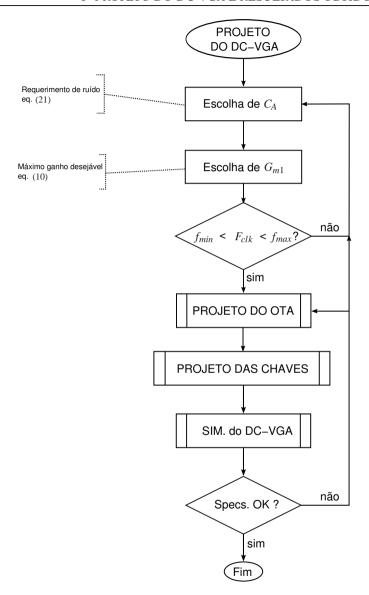

| 22  | Diagrama de fluxo que descreve o procedimento adotado                                                                                  |    |

|     | no projeto do DC-VGA                                                                                                                   | 68 |

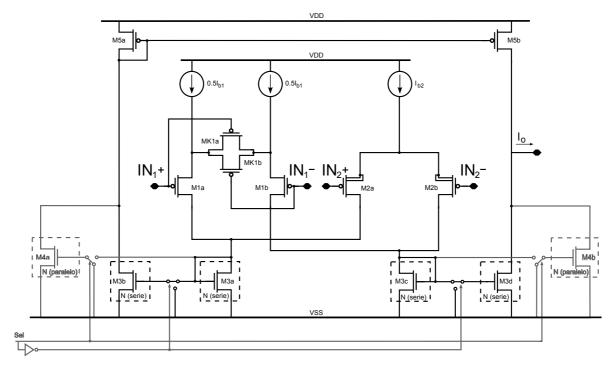

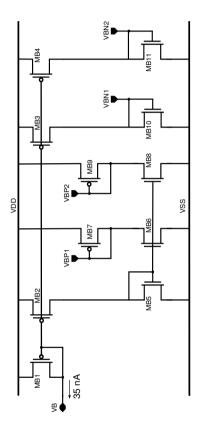

| 23  | Proposta da topologia do OTA de duas entradas e                                                                                        |    |

| 2.4 | transcondutância programável.                                                                                                          | 71 |

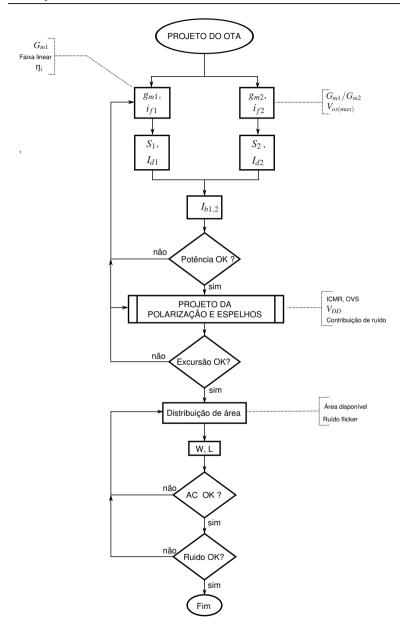

| 24  | Diagrama de fluxo que descreve o procedimento adotado                                                                                  | 7. |

| 25  | no projeto do OTA                                                                                                                      | 75 |

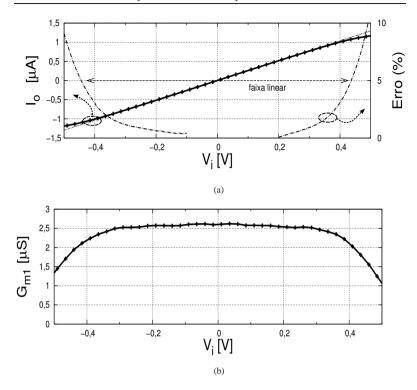

| 25  | Faixa linear do OTA em função a uma tensão diferencial na entrada <i>IN</i> <sub>1</sub> : calculada a partir da (a) corrente de saída |    |

|     | medida e o erro referenciado à resposta de um OTA ideal.                                                                               |    |

|     | Também é mostrada em (b) a transcondutância calculada                                                                                  |    |

|     | a partir da derivada da corrente medida                                                                                                | 79 |

|     | a parair ou derivada da corrente intendad                                                                                              | 1) |

|     |                                                                                                                                        |    |

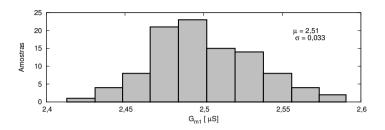

| 26 | Histograma do valor de $G_{m1}$ a partir da análise de Monte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20 | Carlo feito para 100 simulações, considerando variações                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    | de processo e descasamento.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80 |

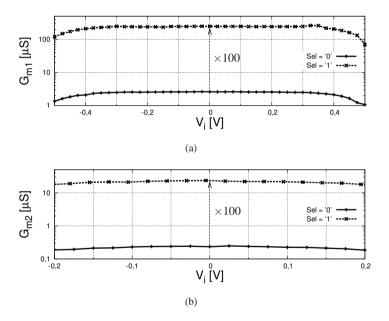

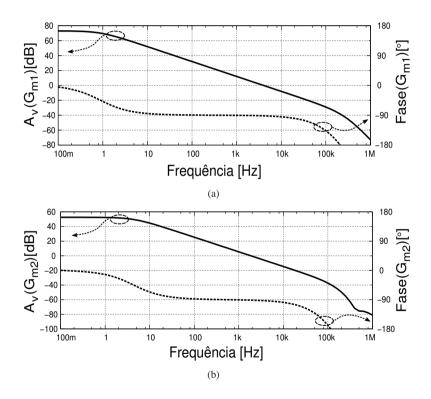

| 27 | Valores medidos das transcondutâncias (a) $G_{m1}$ e (b) $G_{m2}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80 |

| 21 | para ambas as configurações de transcondutância (através                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|    | do seletor <i>Sel</i> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 |

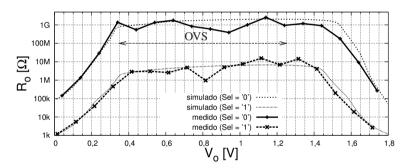

| 28 | Cálculo da OVS a partir da medição da impedância                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 |

| 20 | de saída do OTA para ambas as configurações de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|    | $G_{m1} = 2.5 \mu\text{S}$ (a) e $G_{m1} = 250 \mu\text{S}$ (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81 |

| 29 | Resposta simulada em frequência referente à entrada (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01 |

| 23 | $IN_1$ e (b) $IN_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82 |

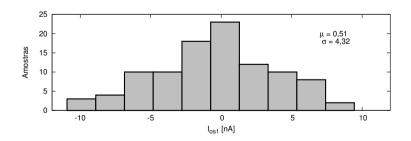

| 30 | Histograma da corrente de <i>offset</i> para a estimativa da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 02 |

| 30 | tensão de <i>offset</i> referida à entrada a partir de 100 simulações.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83 |

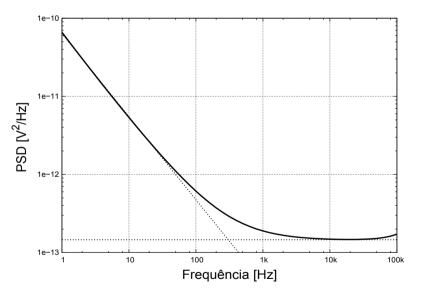

| 31 | Densidade espectral de potência do ruído referido à                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 03 |

| 31 | entrada IN <sub>1</sub> a partir de simulação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84 |

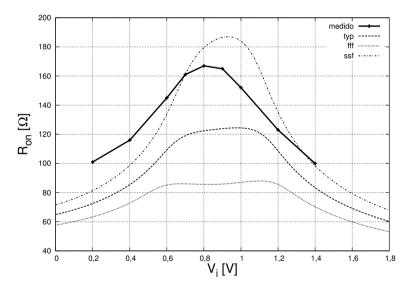

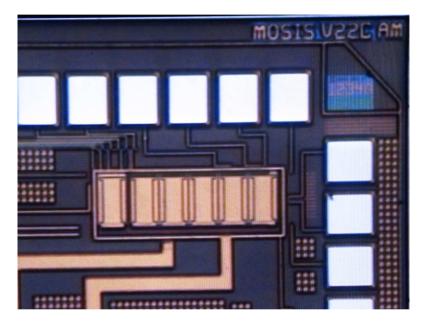

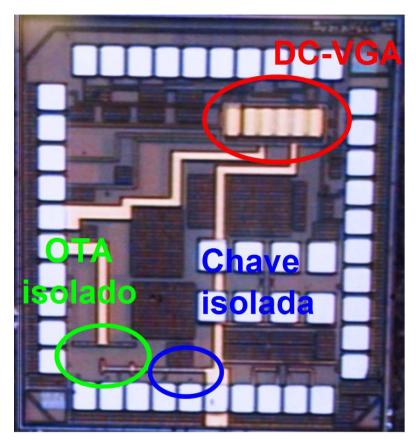

| 32 | Comparação de resultados de simulação e de medição da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0- |

| 32 | resistência equivalente numa das chaves caracterizadas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | quando encontra-se fechada.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85 |

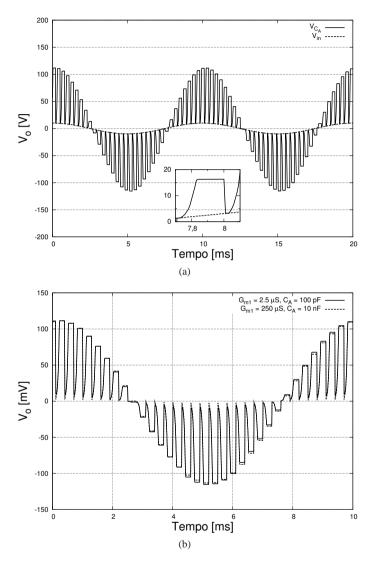

| 33 | Tensão de saída do DC-VGA simulada para (a) $G_{m1} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 05 |

| 33 | 2,5 $\mu$ S e (b) ambas as configurações de $G_{m1}$ , com $T_A =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|    | $2.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (b) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as configurações de $3.5 \mu$ s c (c) almoss as c (c) almo | 87 |

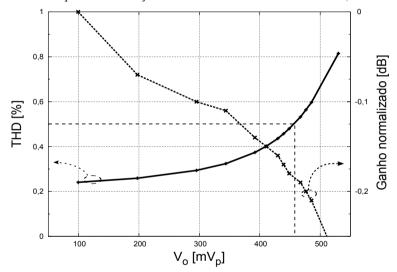

| 34 | Cálculo da faixa linear de operação do DC-VGA em                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 07 |

| 34 | função à THD, a partir de simulações com o sinal de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|    | entrada em 100Hz e variando a sua amplitude de 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|    | a 55 mV <sub>D</sub> , para $T_A = 100 \mu s$ . A variação do ganho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|    | normalizado ao valor de $V_o = 100 \mathrm{mV_p}$ também é mostrada.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88 |

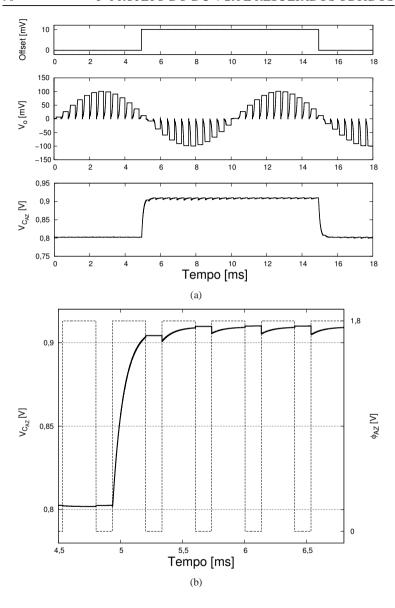

| 35 | Teste de funcionamento da técnica de <i>Auto-Zero</i> a partir de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00 |

| 33 | simulações: Acima, tensão de <i>offset</i> aplicada na entrada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

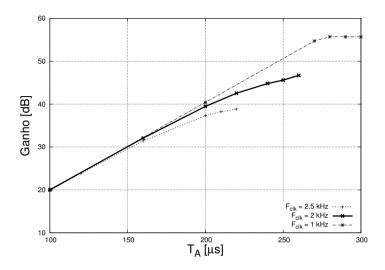

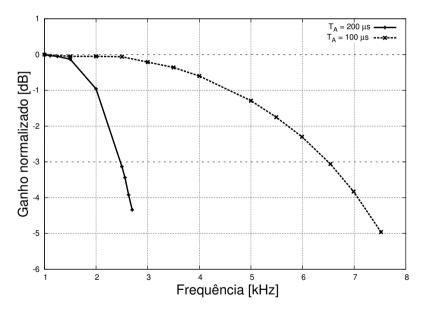

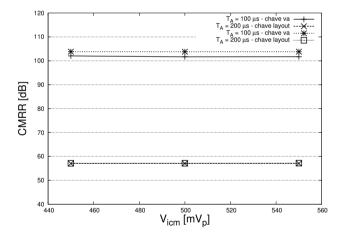

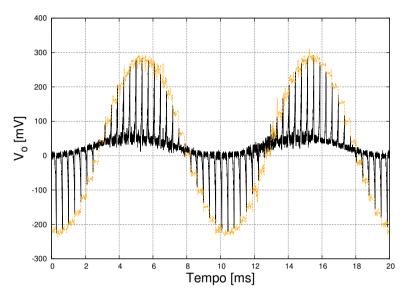

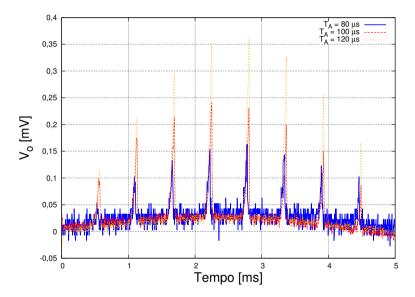

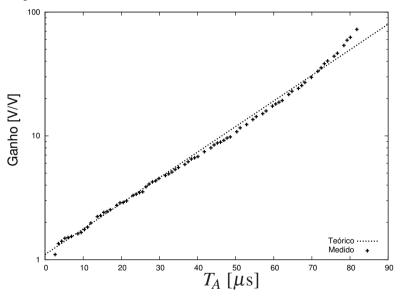

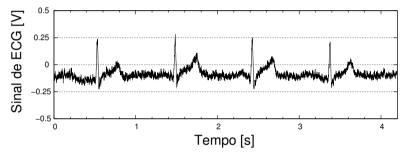

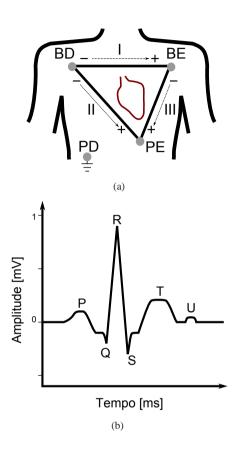

|    | $IN_1$ , no meio, tensão de saída do DC-VGA, embaixo,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |