RÉPUBLIQUE FRANÇAISE

#### **INSTITUT NATIONAL** DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

(11) N° de publication :

2 876 517

(à n'utiliser que pour les commandes de reproduction)

N<sup>o</sup> d'enregistrement national :

04 10644

(51) Int Cl<sup>8</sup>: **H 04 B 1/30** (2006.01), H 04 L 27/18, G 06 G 7/22

#### DEMANDE DE BREVET D'INVENTION

Α1

- 22) **Date de dépôt** : 08.10.04.

- Priorité:

- Demandeur(s) : GROUPE DES ECOLES DES TELE-COMMUNICATIONS Etablissement public à caractère administratif - FR.

- Date de mise à la disposition du public de la demande: 14.04.06 Bulletin 06/15.

- (56) Liste des documents cités dans le rapport de recherche préliminaire : Se reporter à la fin du présent fascicule

- (60) Références à d'autres documents nationaux apparentés:

- (72) Inventeur(s): HUYART BERNARD et RANGEL DE SOUSA FÈRNANDO.

- (73**)** Titulaire(s) :

- (74) Mandataire(s): CABINET HIRSCH POCHART ET ASSOCIES.

- DEMODULATEUR ET MODULATEUR-DEMODULATEUR PAR CONVERSION DIRECTE DE FREQUENCE.

Le démodulateur par conversion directe de fréquence, comprend un dispositif d'addition vectorielle présentant:

- un premier circuit (1) fournissant, à partir d'un premier signal alternatif (LO), un signal alternatif respectif sur n sortion qui cont tous de même amplitude et de même fréquence. ties qui sont tous de même amplitude et de même fréquence mais déphasés entre eux pour que chacun soit ni en

phase ni en opposition de phase avec aucun autre; - un deuxième circuit (2) divisant un deuxième signal alternatif (RFin) vers n sorties; et

- un nombre n de sommateurs (3a, 3b, 3c) recevant chacun en entrée une sortie respective du premier circuit (1) et une sortie respective du deuxième circuit (2);

- un capteur de puissance respectif (4a, 4b, 4c) pour chaque sommateur:

Le nombre n est supérieur ou égal à 3.

Il comprend de plus des moyens de traitement numérique (5, 6) fournissant le résultat de la démodulation.

# DEMODULATEUR ET MODULATEUR-DEMODULATEUR PAR CONVERSION DIRECTE DE FREQUENCE

La présente invention concerne le domaine des applications radiofréquences, notamment celui de la radiocommunication avec fréquence porteuse et des émetteurs- récepteurs par conversion directe de fréquence. L'invention concerne plus particulièrement un démodulateur et un modulateur-démodulateur aptes à être utilisés notamment dans de tels émetteurs-récepteurs.

Les récepteurs par conversion directe de fréquence — dits aussi homodynes — sont devenus aujourd'hui répandus en raison de la simplicité des circuits qui permet de limiter les coûts en comparaison des architectures hétérodynes. Son principe est basé sur la décomposition vectorielle du signal modulé reçu. Puisque les signaux modulés reçus sont complètement caractérisés par leurs enveloppes complexes, une base définie par deux vecteurs orthogonaux — dite base cartésienne — est suffisante pour les représenter. Cependant, il est très difficile de réaliser un circuit de deux voies garantissant l'orthogonalité entre deux signaux dans un intervalle de fréquence important tel qu'utilisé dans les systèmes à large bande et/ou à bande multiple.

Des récepteurs par conversion directe de fréquence plus adaptés aux systèmes à large bande et/ou bande multiple sont les récepteurs cinq ou six ports, voir plus, qui fournissent à partir de deux entrées, au moins trois signaux en sortie à partir desquels on peut estimer les composantes cartésiennes de l'enveloppe complexe du signal modulé reçu. Ces systèmes permettent de s'affranchir des contraintes d'orthogonalité des récepteurs cartésiens grâce à une procédure de calibrage dans toute la bande de fréquence d'opération.

De façon similaire, il existe pour les liaisons montantes des émetteurs à conversion directe de fréquence recourant à des modulateurs à deux voies transportant les signaux de base cartésienne. Il a aussi été proposé des modulateurs à base de trois vecteurs.

De tels récepteurs ou émetteurs par conversion directe de fréquence fournissant trois signaux de sorties ou plus sont présentés dans les documents suivants :

- EP-A-0 805 561 décrit un démodulateur basé sur une jonction à six accès, des détecteurs de puissance et un circuit de traitement analogique pour retrouver les composantes cartésiennes I et Q de l'enveloppe complexe du signal reçu.

- US-A-6,650,178 un récepteur par conversion directe avec au moins trois accès.

Ce circuit utilise deux circuits interféromètriques passifs reliés par un élément déphaseur. L'information portée par le signal reçu est récupérée à partir des

5

10

15

20

25

- mesures de puissance réalisées aux accès de sortie des jonctions interféromètriques.

- US-A-5,498,969 décrit une architecture de jonction à six accès appliquée à un dispositif de mesure vectorielle avec un circuit diviseur de puissance, d'un circuit déphaseur, un capteur de puissance adapté et trois autres non-adaptés.

- EP-A-0 841 756 décrit un récepteur six-port utilisant un circuit corrélateur dans lequel le signal modulé reçu est sommé à quatre signaux issus de l'oscillateur de référence, mais déphasés entre eux à chaque fois de 90°. Les valeurs des composantes cartésiennes du signal en bande de base sont trouvées par un circuit analogique à partir des puissances des signaux RF.

- US-A-5,095,536 décrit un récepteur par conversion directe basé sur une architecture triphasée et trois circuits mélangeurs. Le signal de référence est divisé en trois voies déphasées qui sont ensuite mélangées avec le signal modulé reçu. L'information est récupérée par traitement numérique des signaux fournis aux sorties de filtres et d'amplificateurs placés après les mélangeurs.

- F. Ellinger, U. Lot et W. Bächtold décrivent un circuit modulateur qui utilise une base vectorielle de trois vecteurs linéairement dépendants dans le document intitulé "An antenna Diversity MMIC Vector Modulator for HIPERLAN with Low Power Consuption and Calibration Capability" paru dans les pages 964-969 du journal IEEE Transactions on Microwave Theory and Technique, Vol. 49, N. 5, 2001.

- L'article "A 1.4 2.7 GHz Analog MMIC Vector Modulator for a Crossbar Beamforming Network" de J. Grajal, M. Mahfoudi, J. Gismero et F.A. Petz,paru dans les pages 1705-1714 du journal IEEE Transactions on Microwave Theory and Technique, Vol. 45, N. 10, 1997, décrit un modulateur vectoriel utilisant trois vecteurs déphasés de 120°.

Le but de l'invention est de proposer une nouvelle technologie de démodulation, voire de modulation et démodulation, par conversion directe de fréquence qui soit d'une mise en œuvre simple et économique, qui puisse notamment être mise en œuvre à des fréquences élevées telles que les hyperfréquences tout en permettant d'être intégrée plus facilement que les technologies existantes et qui soit capable d'opérer dans de large bande de fréquence si cela est souhaitable.

A cette fin, la présente invention propose d'abord un dispositif d'addition vectorielle de deux signaux électriques alternatifs modulés ou non, comprenant :

5

10

15

20

25

- une première entrée pour recevoir un premier signal électrique alternatif;

- une deuxième entrée pour recevoir un deuxième signal électrique alternatif;

- un premier circuit relié à la première entrée et comprenant un nombre n de sorties, le premier circuit fournissant, à partir du premier signal alternatif appliqué à la première entrée, un signal alternatif respectif sur chacune des n sorties, lesdits signaux alternatifs fournis sur les n sorties étant tous de même amplitude et de même fréquence mais déphasés entre eux pour que chacun soit ni en phase ni en opposition de phase avec aucun autre ;

- un deuxième circuit relié à la deuxième entrée et comprenant un même nombre n de sorties, le deuxième circuit divisant le deuxième signal alternatif vers ses n sorties ; et

- un même nombre n de sommateurs recevant chacun en entrée une sortie respective du premier circuit et une sortie respective du deuxième circuit ;

dans lequel le nombre n est supérieur ou égal à 3.

Suivant des modes de réalisation préférés, l'invention comprend une ou plusieurs des caractéristiques suivantes :

- chacun des signaux alternatifs fournis par le premier circuit sur ses n sorties est déphasé par rapport à chacun des autres signaux alternatifs fournis par le premier circuit sur ses n sorties de 20° à 160° en avance ou en retard ;

- les sommateurs comprennent chacun deux transistors montés en amplificateur différentiel ;

- le premier circuit comprend un même nombre n d'amplificateurs, l'entrée de chacun des amplificateurs étant reliée à la première entrée et la sortie de chacun des amplificateurs étant ensuite relié à un circuit de déphasage respectif.

- le nombre n est égal à 3

10

15

20

25

30

- chacun des signaux alternatifs fournis par le premier circuit sur ses trois sorties est déphasé par rapport à chacun des deux autres signaux alternatifs fournis par le premier circuit sur ses trois sorties par un angle de 80° à 160° en avance ou en retard ;

- chacun des signaux alternatifs fournis par le premier circuit sur ses trois sorties est déphasé par rapport à chacun des deux autres signaux alternatifs fournis par le premier circuit sur ses trois sorties par un angle de 120° en avance ou en retard;

- la sortie de chacun des sommateurs est reliée à un capteur de puissance respectif.

L'invention propose aussi un démodulateur par conversion directe de fréquence, comprenant :

- un dispositif d'addition vectorielle selon l'invention ;

- un même nombre n de convertisseurs analogique/numérique relié chacun à un capteur de puissance respectif ; et

- un circuit de traitement numérique déterminant les composantes cartésiennes de l'enveloppe complexe du signal appliqué à la deuxième entrée du dispositif d'addition vectoriel à partir des mesures fournies par les n capteurs de puissance.

L'invention propose aussi un récepteur RF, comprenant :

- un démodulateur selon l'invention;

- un oscillateur local relié à la première entrée du dispositif d'addition vectorielle ;

- une antenne de réception RF; et

5

15

20

25

30

- un amplificateur du signal reçu par l'antenne pour l'appliquer à la deuxième entrée du dispositif d'addition vectorielle.

L'invention propose encore un modulateur-démodulateur par conversion directe de fréquence, comprenant un démodulateur selon l'invention et dans lequel le modulateur comprend :

- un même nombre n d'amplificateurs à gain variable, l'entrée de chaque amplificateur étant reliée à une sortie respective du premier circuit du dispositif d'addition vectorielle ;

- un sommateur recevant en entrée la sortie de chacun des n amplificateurs à gain variable ;

- un circuit de traitement numérique fournissant un même nombre n de commandes de gain d'amplificateur à partir des composantes cartésiennes de l'enveloppe complexe à fournir par modulation ; et

- un même nombre n de convertisseurs numériques/analogiques, l'entrée de chacun étant reliée au circuit de traitement numérique et la sortie de chacun étant reliée à l'entrée de commande de gain d'un amplificateur respectif.

Le modulateur-démodulateur peut avantageusement comprendre un circuit permettant de relier sélectivement la deuxième entrée du circuit d'addition vectorielle à la sortie du sommateur recevant en entrée la sortie de chacun des n amplificateurs à gain variable.

L'invention propose encore un émetteur-récepteur, comprenant :

- un modulateur-démodulateur selon l'invention;

- un oscillateur local reliée à la première entrée du dispositif d'addition vectorielle ; et

- au moins une antenne RF et au moins un amplificateur pour alimenter la deuxième entrée du dispositif d'addition vectorielle et pour émettre le signal obtenu à la sortie du sommateur relié aux n amplificateurs à gain variable.

L'invention propose aussi un procédé de calibration du modulateur d'un modulateur-démodulateur selon l'invention à une fréquence donnée, le démodulateur ayant été préalablement calibré à la fréquence donnée, le procédé comprenant les étapes de :

- application d'un signal alternatif à la fréquence donnée à la première entrée du dispositif d'addition vectorielle ;

- mise en liaison de la deuxième entrée du circuit d'addition vectorielle à la sortie du sommateur recevant en entrée la sortie de chacun des n amplificateurs à gain variable ;

- génération par le modulateur de signaux modulés à partir des composantes cartésiennes d'enveloppe complexe de signaux ;

- comparaison des composantes cartésiennes d'enveloppe complexe fournis par le démodulateur en conséquence de l'étape précédente avec les composantes cartésiennes d'enveloppe complexe de signaux ayant servi à la génération des signaux modulés; et

- calibration du modulateur en fonction des résultats de l'étape précédente.

L'invention propose enfin un procédé de calibration du démodulateur d'un modulateur-démodulateur selon l'invention à une fréquence donnée, le modulateur ayant été préalablement calibré à la fréquence donnée, le procédé comprenant les étapes de :

- application d'un signal alternatif à la fréquence donnée à la première entrée du dispositif d'addition vectorielle ;

- mise en liaison de la deuxième entrée du circuit d'addition vectorielle à la sortie du sommateur recevant en entrée la sortie de chacun des n amplificateurs à gain variable ;

- génération par le modulateur de signaux modulés à partir des composantes cartésiennes d'enveloppe complexe de signaux ;

- comparaison des composantes cartésiennes d'enveloppe complexe fournis par le démodulateur en conséquence de l'étape précédente avec les composantes cartésiennes d'enveloppe complexe de signaux ayant servi à la génération des signaux modulés; et

- calibration du démodulateur en fonction des résultats de l'étape précédente.

D'autres caractéristiques et avantages de l'invention apparaîtront à la lecture de la description qui suit d'un mode de réalisation préféré de l'invention, donnée à titre d'exemple et en référence au dessin annexé.

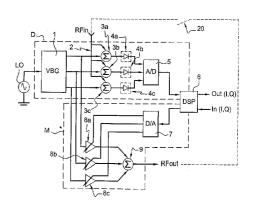

La figure 1 est une illustration dans le plan de Fresnel des signaux électriques existants dans un dispositif d'addition vectorielle selon l'invention.

5

10

15

20

25

30

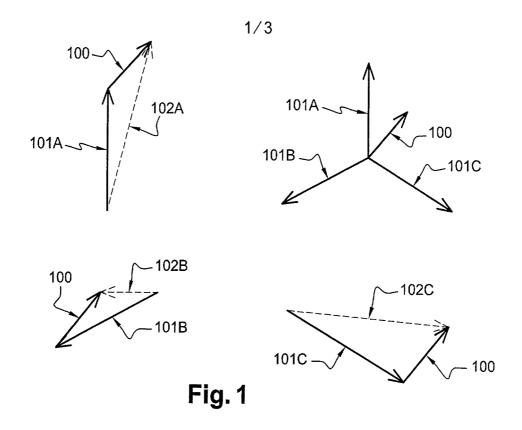

La figure 2 est un schéma synoptique d'un émetteur-récepteur mettant en œuvre l'invention.

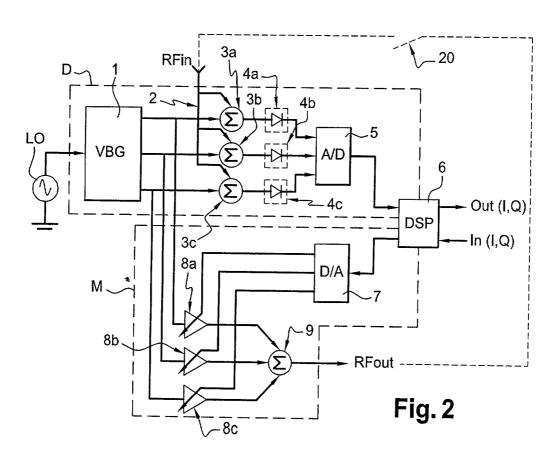

La figure 3 est un schéma électronique d'un mode de réalisation particulier d'un émetteur-récepteur selon l'invention.

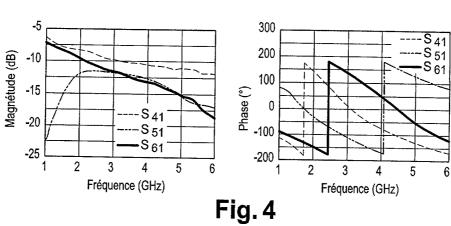

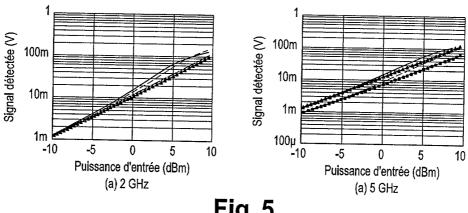

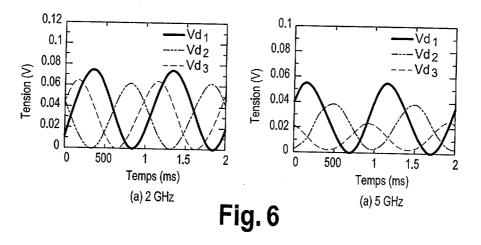

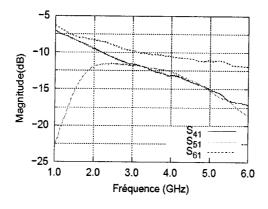

Les figures 4 à 6 illustrent les résultats obtenus avec le circuit décrit en référence à la figure 3.

Le dispositif d'addition vectorielle de deux signaux électriques alternatifs selon l'invention comprend une première entrée pour recevoir un premier signal électrique alternatif et une deuxième entrée pour recevoir un deuxième signal électrique alternatif. Il comprend un premier circuit relié à la première entrée et comprenant un nombre n de sorties, le premier circuit fournissant, à partir du premier signal alternatif appliqué à la première entrée, un signal alternatif respectif sur chacune des n sorties, lesdits signaux alternatifs fournis sur les n sorties étant tous de même amplitude et de même fréquence mais déphasés entre eux. Ces signaux alternatifs fournis sur les n sorties sont déphasés de façon que chacun soit ni en phase ni en opposition de phase avec aucun autre d'entre eux. Autrement dit, dans le plan de Fresnel, aucun des vecteurs correspondants est colinéaire avec un autre de ces vecteurs. Le nombre n est supérieur ou égal à 3.

Il comprend encore un deuxième circuit relié à la deuxième entrée et comprenant le même nombre n de sorties, le deuxième circuit divisant le deuxième signal alternatif vers ses n sorties. Enfin, il comprend le même nombre n de sommateurs recevant chacun en entrée une sortie respective du premier circuit et une sortie respective du deuxième circuit.

Ce dispositif permet notamment de fournir plusieurs signaux résultants de la somme d'un même signal alternatif avec un autre signal alternatif de même fréquence à chaque fois déphasé selon un autre angle, ce qui permet ensuite de comparer les deux signaux sur la base des signaux résultants.

Dans le plan de Fresnel, le premier signal fournit une sorte de base vectorielle définie par n vecteurs, chacun étant ensuite additionné au deuxième signal. La figure 1 illustre cette situation avec le nombre n égal à 3, la référence 100 indiquant le vecteur correspondant au deuxième signal qui est additionné plusieurs fois au premier signal à chaque fois déphasé en l'occurrence de 120° et dont les vecteurs sont indiqués par 101A, 101B et 101C. Les vecteurs résultants des sommes sont référencés 102A, 102B et 102C.

Un tel dispositif d'addition permet avantageusement de comparer deux signaux alternatifs de même fréquence tant du point de vue de leur phase que de leur amplitude. Pour cela, il suffit d'appliquer l'un à la première entrée du dispositif et l'autre à la deuxième entrée du dispositif. En particulier, la comparaison peut être

5

10

15

20

25

30

effectuée sur la base des modules des vecteurs résultants qui peuvent être mesurés par un capteur de puissance respectif. Le fait que les signaux des n sorties du premier circuit ne sont ni en phase ni en opposition de phase entre eux permet d'assurer que chaque « projection » du vecteur de Fresnel correspondant au deuxième signal sur les vecteurs de Fresnel du premier signal ainsi déphasé soit à chaque fois différente et que notamment l'une de ces « projections » comporte une proportion importante des composantes réelle et imaginaire du vecteur correspondant au deuxième signal. Ceci est avantageux par rapport au cas où le signal est divisé en quatre signaux déphasés à chaque fois de 90° comme c'est le cas dans EP-A-0 841 756 car lorsque la phase du signal est proche de celle d'un des quatre vecteurs correspondants, l'estimation d'une des composantes est faible et par conséquent l'incertitude plus importante.

Il est préférable que les signaux alternatifs fournis sur les n sorties du premier circuit soient chacun déphasé par rapport à tous les autres de ces signaux d'un angle compris dans l'intervalle de 20° à 160°, bornes comprises, peu importe que ce soit en avance ou en retard. Autrement dit, dans le plan de Fresnel, la direction du vecteur correspondant à l'un quelconque de ces signaux forme un angle d'au moins 20° par rapport à la direction du vecteur correspondant à n'importe lequel de ces autres signaux. Cela permet d'obtenir une sensibilité suffisante pour effectuer la comparaison. De ce point de vue, il est avantageux de choisir dans le cas où n égal à trois une configuration pour laquelle chaque signal de sortie du premier circuit soit déphasé de +120° et -120° par rapport aux deux autres signaux de sorties.

Ce dispositif trouve avantageusement application lorsqu'un signal incident est comparé à un signal réfléchi pour déterminer un facteur de réflexion, par exemple dans l'analyse de réseaux électriques. Similairement, il trouve application pour la détermination de facteur de transmission à partir d'un signal incident et du signal transmis pour mettre en œuvre un discriminateur pour radar.

Ce dispositif permet aussi de mettre en œuvre un démodulateur par conversion directe de fréquence en appliquant à la deuxième entrée le signal modulé et à la première entrée le signal d'un oscillateur local réglé en fréquence sur celle du signal modulé. Il s'agit de préférence de modulation numérique, mais la modulation analogique est également possible. Préférentiellement, il s'agit de modulation en phase et/ou amplitude, mais la modulation de fréquence est également possible. Le fait de recourir à des sommateurs suivis de détecteurs quadratiques est avantageux par rapport à l'utilisation de mélangeurs comme dans US-A-5,095,536 étant donné que ces derniers sont plus complexes et plus chers.

Le fait d'avoir le nombre n au moins égal à trois permet de fournir une redondance d'information permettant la correction des défauts du système. D'abord, le troisième vecteur permet d'éliminer l'ambiguïté due à la détection quadratique par

5

10

15

20

25

30

mesure de puissance. Ensuite, cette redondance s'avère utile aussi pour réduire l'impact des imperfections des circuits qui apparaissent sous la forme de désappariement de phase et gain, causant une distorsion sur la constellation du signal démodulé.

Le cas où le nombre n est égal à trois est avantageux en raison de sa simplicité de mise en œuvre et son coût limité par rapport au cas où ce nombre est supérieur à trois comme dans le cas de EP-A-0 841 756. Idéalement, les trois signaux fournis en sortie par le premier circuit sont déphasés de 120° afin de maximiser les « projections »du deuxième signal sur les différents vecteurs de cette base vectorielle. Plus on s'éloigne de ce cas idéal, plus la précision de la comparaison en pratique se dégrade, mais la comparaison reste possible même dans le cas où le déphasage n'est plus que de l'ordre de 20°.

Nous allons décrire maintenant un émetteur-récepteur mettant en œuvre l'invention un dispositif d'addition vectorielle à trois voies (c'est-à-dire avec le nombre n égal à trois) en référence à la figure 2.

La partie récepteur de l'émetteur-récepteur comprend un démodulateur D, un oscillateur local LO et une antenne de réception du signal modulé RFin.

Le démodulateur D comprend un générateur de base vectorielle 1, un circuit diviseur de signaux RF 2, de trois sommateurs de signaux RF 3a, 3b et 3c, de trois capteurs de puissance 4a, 4b et 4c, d'un bloc de conversion analogique/numérique 5 et d'un circuit de traitement numérique 6.

Comme cela apparaîtra de la description ci-dessous, le générateur de base vectorielle 1, le circuit diviseur de signaux RF 2 et les trois sommateurs de signaux RF 3a, 3b et 3c constituent un dispositif d'addition vectorielle comme décrit précédemment.

Le démodulateur D reçoit en entrée le signal modulé RFin et le signal alternatif d'un oscillateur local LO qui sert de référence.

Le signal de l'oscillateur local LO est appliqué en entrée du générateur de base vectorielle 1. A partir de ce signal, le générateur de base vectorielle 1 fournit en sortie trois signaux alternatifs de même fréquence et de même amplitude, mais qui sont déphasés entre eux, chacun des trois signaux étant fourni sur une voie distincte. Chacune des trois voies est reliée à une entrée d'un sommateur respectif 3a, 3b et 3c. Le déphasage entre les trois signaux peut être obtenus à l'aide de filtres passifs ou actifs, de lignes de transmission ou tout autre circuit fournissant un déphasage à un signal dans l'intervalle de fréquence de fonctionnement du démodulateur.

Le signal modulé RFin est amplifié par un amplificateur à faible bruit, non représenté, avant d'être appliqué au circuit diviseur 2. Le circuit diviseur 2 divise le signal modulé RFin vers trois voies distinctes sans introduire de déphasage entre

5

10

15

20

25

30

elles ni de différence d'amplitude. Chacune de ces trois voies est reliée à l'entrée d'un sommateur respectif 3a, 3b et 3c. Le circuit diviseur 2 est représenté symboliquement sur la figure 1 par une branche d'entrée sur laquelle sont reliées trois branches connectées chacune à une entrée d'un sommateur respectif 3a, 3b et 3c. En pratique, le circuit diviseur 2 peut être mis en œuvre par la mise en parallèle des transistors avec leurs circuits d'adaptation et de polarisation, ce qui a l'avantage de permettre l'intégration du circuit et procurer une large bande de fonctionnement par rapport aux structures classiques à base de lignes de propagation telles que les diviseurs de Wilkinson.

Chacun des sommateurs 3a, 3b et 3c fournit donc en sortie un signal correspondant à l'addition du signal fourni par une voie respective du générateur de base vectorielle 1 et du signal RFin après division. La puissance du signal de sortie de chaque sommateur 3a, 3b et 3c est mesurée par un capteur de puissance respectif 4a, 4b et 4c qui fournit en sortie un signal analogique représentatif de la puissance du signal. Préférentiellement, chaque capteur de puissance 4a, 4b et 4c est mis en œuvre par un élément non linéaire telle qu'une diode Schottky, suivi d'un filtre passe-bas pour éliminer les composantes du signal autres que celles de la bande de base.

Le signal analogique fourni par chaque capteur de puissance 4a, 4b et 4c est ensuite converti en signal numérique par le bloc de conversion analogique/numérique 5, le signal numérique étant fourni au circuit de traitement numérique 6. Avant conversion numérique, ce signal analogique peut éventuellement être conditionné par un circuit amplificateur de gain ajustable et/ou un circuit de compensation du décalage en tension ou courant continu. Le bloc de conversion analogique/numérique 5 est mis en œuvre par un convertisseur analogique/numérique respectif pour chaque capteur de puissance 4a, 4b et 4c, avec l'échantillonnage de ces convertisseurs étant simultanée pour assurer la cohérence des trois voies de mesure.

En fonctionnement, la fréquence de l'oscillateur local LO est calée sur celle du signal modulé RFin.

Le circuit de traitement numérique 6 détermine les composantes cartésiennes de l'enveloppe complexe – référencées par Out (I, Q) sur la figure 1 - du signal modulé RFin par traitement numérique des signaux représentatifs des puissances mesurées par les capteurs de puissance 4a, 4b et 4c. Autrement dit, le circuit de traitement numérique 6 fournit le signal démodulé. Le circuit de traitement numérique peut classiquement comprendre un microprocesseur.

Le traitement numérique peut être basé sur un algorithme approprié et/ou sur une table de conversion telle que par exemple décrit par F. R. de Sousa, B. Huyart, S. Y. C. Catunda et R. N. de Lima dans «A to D Converters and Look-up Tables Dimensioning for Five-Port Reflectometer Based Systems» paru dans les actes de la

10

15

20

25

30

conférence de la société *Instrumentation and measurement* du IEEE , 2003, p. 743-747 incorporé par référence dans la présente demande.

Ce traitement numérique est basé sur les fonctions de transfert des différentes voies du démodulateur, notamment des déphasages et atténuations introduit par le générateur de base vectorielle 1, par le circuit diviseur 2 et les sommateurs 3a, 3b et 3c ainsi que les défauts de linéarité des capteurs de puissance 4a, 4b et 4c. Par ailleurs, ces fonctions de transfert varient généralement en fonction de la fréquence à laquelle le démodulateur travaille.

Les paramètres de la fonction de transfert peuvent être déterminés par une procédure de calibration similaire à celles utilisées dans l'art antérieur pour les récepteurs cinq ports ou similaires. Par exemple, des séquences de signaux modulés prédéterminés sont envoyées par une station de base à l'émetteur-récepteur qui a préalablement en mémoire les composantes cartésiennes I et Q – respectivement la partie réelle et la partie imaginaire - correspondantes à l'enveloppe complexe de ces signaux. Après démodulation, le circuit de traitement numérique 6 calcule les constantes de calibrage afin que les composantes cartésiennes obtenues par la démodulation soient identiques à celles en mémoire, permettant ainsi de calibrer le démodulateur D en fonction des écarts constatés.

Pour parachever la partie récepteur, le circuit de traitement numérique 6 peut en outre procéder au décodage du signal démodulé avant d'être restitué de façon classique.

Nous allons décrire ci-dessous un modèle mathématique de fonctionnement du démodulateur D. Le générateur de base vectorielle 1 fournit trois signaux pouvant chacun être exprimés comme suit :

$$v_{LOi}(t) = \sqrt{a_i} \cdot V_{LO} \cdot \cos(\omega t + \gamma_i)$$

(1)

avec:

10

15

20

30

- $V_{LO}$  et  $\omega$  : respectivement l'amplitude et la pulsation du signal fourni par l'oscillateur local LO ;

- $\gamma_i$ : la phase relative sur la voie de sortie i considérée du générateur de base vectorielle 1 ; et

- √a<sub>i</sub>: le gain de la voie de sortie i considérée du générateur de base vectorielle 1.

Le circuit diviseur 2 fournit trois signaux s'exprimant chacun par :

$$v_{RFi}(t) = \sqrt{b_i \cdot V_{RF}(t) \cdot \cos(\omega t + \theta(t) + \lambda_i)}$$

(2)

35 avec:

- $V_{RF}(t)$ ,  $\theta(t)$  et  $\omega$ : respectivement l'amplitude instantanée, la phase instantanée et la pulsation du signal modulé RFin reçu en entrée :

- $\lambda_i$ : la phase relative du signal sur la voie de sortie i du diviseur 2 ; et

-  $\sqrt{b_i}$ : le gain de la voie de sortie i considérée du diviseur 2.

5

10

20

30

Dans le cas de capteurs de puissance 4a, 4b et 4c fonctionnant comme des détecteurs quadratiques, chacun fournit en sortie un signal représenté par l'équation suivante :

$$v_{i}(t) = a_{i} \cdot V_{LO}^{2} + b_{i} \cdot V_{RF}(t)^{2} + c_{i} \cdot V_{RF}(t) \cdot \cos(\theta(t) - \phi_{i})$$

(3)

dans laquelle  $\phi_i = \gamma_i \cdot \lambda_i$ ,  $c_i$  est dépendant de  $a_i$  et  $b_i$ ,  $V_{LO}$  qui est supposé constant , $a_i$ ,  $b_i$ ,  $\gamma_i$  et  $\lambda_i$  les paramètres mentionnés ci-dessus dans les équations 1 et 2.

Les composantes de la bande de base, à savoir la partie réelle  $I(t) = V_{RF}(t).\cos\theta(t)$  et la partie imaginaire  $Q(t) = V_{RF}(t).\cos\theta(t)$ , sont déterminées par une combinaison linéaire des signaux  $v_i(t)$  fournis par les capteurs de puissance 4a, 4b et 4c pondérés par les constantes de calibration comme le montre les équations cidessous:

$$I(t) = \sum_{i=1}^{n} \alpha_i \nu_i(t) + \kappa_I \tag{4}$$

$$Q(t) = \sum_{i=1}^{n} \beta_i v_i(t) + \kappa_Q \tag{5}$$

dans lesquelles n est le nombre sorties du circuit d'addition vectorielle et  $\alpha_i$ ,  $\beta_i$ ,  $\kappa_i$  et  $\kappa_Q$  sont des constantes dépendantes des valeurs de  $a_i$ ,  $b_i$ ,  $\gamma_i$ ,  $\lambda_i$  et  $V_{LO}$

La procédure de calibrage mentionnée auparavant consiste donc à déterminer  $\alpha_i$ ,  $\beta_i$ ,  $\kappa_I$  et  $\kappa_Q$ . En occurrence, pour n=3, ces constantes sont exprimées en fonction des paramètres  $a_i$ ,  $b_i$  et  $c_i$  à partir d'une inversion matricielle du système de trois équations reliant les 3 données de mesure  $v_3'(t)$ ,  $v_4'(t)$  et  $v_5'(t)$  aux trois inconnues  $V_{RF}(t)^2$ , I(t), Q(t) ci-dessous:

25

$$v_3'(t) = b_3 \cdot V_{RF}(t)^2 + c_3 \cdot \cos \phi_3 I(t) + c_3 \cdot \sin \phi_3 Q(t)$$

$$v_4'(t) = b_4 \cdot V_{RF}(t)^2 + c_4 \cdot \cos \phi_4 I(t) + c_4 \cdot \sin \phi_4 Q(t)$$

$$v_5'(t) = b_5 \cdot V_{RF}(t)^2 + c_5 \cdot \cos \phi_5 I(t) + c_5 \cdot \sin \phi_5 Q(t)$$

avec

$$v_3'(t) = v_3(t) - a_3 \cdot V_{LO}^2$$

,  $v_4'(t) = v_4(t) - a_4 \cdot V_{LO}^2$ ,  $v_5'(t) = v_5(t) - a_5 \cdot V_{LO}^2$ .

Les variables  $v_3(t)$ ,  $v_4(t)$ ,  $v_5(t)$  sont les tensions analogiques de sortie des capteurs de puissance. Les constantes  $a_i.V_{LO}^2$  peuvent se déterminer avant l'inversion matricielle en faisant des mesures aux sorties des capteurs de puissance avec  $v_{RFi}(t)=0$  et  $v_{LO}(t)=V_{LO}.cos$   $\omega t$ . Des méthodes expérimentales permettant de

résoudre le système d'équation ci-dessus sont bien connues dans la littérature, comme par exemple celle décrite dans l'article de F. R. de Sousa, B. Huyart, et R. N. de Lima intitulé « A new method for automatic calibration of 5-port reflectometers. *Journal of Microwave and Optoelectronics*, vol. 3, N.5, pp.135-144, July 2004 » qui est incorporé par référence dans la présente demande et dans laquelle les constantes sont estimées à partir de deux signaux RF connus légèrement décalés en fréquence et des mesures des tensions aux sorties des détecteurs quadratiques.

La partie émetteur de l'émetteur-récepteur est basée sur un modulateur M. Le modulateur M comprend un circuit de traitement numérique qui peut être commun avec le démodulateur D comme représenté sur la figure 1 par le circuit 6. Il comprend aussi un bloc de conversion numérique/analogique 7 et trois amplificateurs RF à gain ajustable 8a, 8b et 8c et un sommateur de signaux RF 9.

Bien que non compris dans le bloc M sur la figure 1, le modulateur M comprend encore le générateur de base vectorielle 1 qui est donc avantageusement commun avec le démodulateur D. Chacune des trois voies de sortie du VBG 1 est appliquée à l'entrée d'un amplificateur respectif 8a, 8b et 8c.

Le gain de chaque amplificateur est commandé par un signal respectif déterminé par le circuit de traitement numérique 6 à partir des composantes cartésiennes In(I, Q) du signal codé à moduler pour sa transmission. Ce traitement numérique est basé sur les fonctions de transfert de chaque voie du modulateur, notamment des déphasages et atténuations introduit par le générateur de base vectorielle 1 et les défauts de linéarité des amplificateurs 8a, 8b et 8c. Là-aussi, ces fonctions de transfert varient généralement en fonction de la fréquence à laquelle le modulateur travaille.

L'on comprendra que les amplificateurs 8a, 8b et 8c ne travaillent pas nécessairement à un gain supérieur à 1, mais peuvent travailler aussi ou exclusivement à un gain inférieur à 1, c'est-à-dire en atténuateur. Les signaux de commande de gain déterminés par le circuit de traitement numérique 6 sont convertis en signaux analogiques par le bloc de conversion numérique/analogique 7 pour être chacun appliqué à l'entrée de commande d'un amplificateur respectif 8a, 8b et 8c. Le bloc de conversion numérique/analogique 7 est mis en œuvre par un convertisseur numérique/analogique respectif pour chaque amplificateur 8a, 8b et 8c.

La sortie de chaque amplificateur 8a, 8b et 8c est appliquée à une entrée respective du sommateur 9. Par conséquent, le sommateur 9 fournit en sortie le signal modulé RFout qui est la somme des trois signaux fournis par les amplificateurs 8a, 8b et 8c.

5

10

15

20

25

30

Pour parachever l'émetteur, le signal de sortie RFout du modulateur M est ensuite classiquement amplifié et appliqué à une antenne d'émission. Par ailleurs, le codage du signal à transmettre peut être réalisé par le circuit de traitement numérique 6 préalablement à la détermination des signaux de commande de gain des amplificateurs 8a, 8b et 8c.

Aussi bien le dispositif d'addition vectorielle selon l'invention que le démodulateur et le modulateur-démodulateur qui l'incorporent peuvent être mis en œuvre pour travailler à n'importe quelle fréquence, à laquelle fonctionnent le récepteur et l'émetteur-récepteur. Ils sont particulièrement adaptées pour travailler à des fréquences supérieures ou égales à 900MHz et peuvent être utilisées dans des applications large bande ou multibande couvrant plusieurs gigahertz.

Le récepteur et l'émetteur-récepteur selon l'invention peuvent travailler dans différentes bandes de fréquence en calant la fréquence de l'oscillateur local sur la fréquence souhaitée. Dans le cas de l'émetteur-récepteur, l'émission et la réception peuvent se faire à la même fréquence ou à des fréquences différentes en changeant la fréquence de l'oscillateur local en correspondance.

L'invention fournit une solution économique d'émetteur-récepteur apte à travailler en duplex par répartition dans le temps – abrégé par TDD en anglais – étant donné que le générateur de base vectorielle est commun à la partie émettrice et à la partie réceptrice. Il est possible de mettre en œuvre un émetteur-récepteur travaillant en duplex par répartition de fréquence en – abrégé par FDD en anglais – en adjoignant un deuxième générateur de base vectorielle, l'un étant spécifique au démodulateur et l'autre au modulateur.

Par ailleurs, l'émetteur-récepteur peut faire l'objet d'une calibration automatique de son modulateur M après que son démodulateur D ait été calibré. La calibration préalable du démodulateur D peut être effectuée de façon classique, notamment comme décrit plus haut. Un interrupteur commandé 20 – réalisé par exemple par un transistor - permet de relier sélectivement la sortie RFout du modulateur M à l'entrée RFin du démodulateur D. La liaison est représentée en tirets sur la figure 2. Le circuit de traitement numérique 6 comprend en mémoire les composantes cartésiennes de l'enveloppe complexe d'une séquences prédéterminée de signaux. Pour procéder à la calibration du modulateur M, le circuit de traitement numérique 6 provoque la fermeture de l'interrupteur 20. Puis, il fait procéder à la modulation à partir de ces composantes cartésiennes en mémoire en déterminant les commandes de gains pour les amplificateurs 8a, 8b et 8c à partir des paramètres du modulateur M qu'il a en mémoire. Les signaux modulés fournis en sortie par le modulateur M sont ensuite démodulés par le démodulateur D. Le circuit de traitement numérique 6 compare alors les composantes cartésiennes de l'enveloppe

5

10

15

20

25

30

complexe obtenue par démodulation avec les composantes cartésiennes correspondantes en mémoire ayant servi à la modulation. Le circuit de traitement numérique 6 procède alors à la calibration du modulateur M en fonction des écarts constatés lors des comparaisons. Cette calibration est rendue possible du fait que le démodulateur D a été préalablement calibré et donc les écarts constatés lors des comparaisons proviennent seulement de l'erreur sur les paramètres du modulateur M en mémoire dans le circuit de traitement numérique 6.

De la même manière, l'émetteur-récepteur peut faire l'objet d'une calibration automatique de son démodulateur D après que son modulateur M ait été calibré de façon classique.

Ces procédures de calibration automatique peuvent aussi être mises en œuvre même dans le cas où le modulateur (M) et le démodulateur (D) ont chacun leur propre générateur de base vectorielle. Elles peuvent aussi s'appliquer dans les modulateurs-démodulateurs de l'art antérieur.

La figure 3 présente un schéma électronique simplifié de l'émetteur-récepteur de la figure 2 qui a été mis en œuvre en technologie MMIC (circuit intégré monolithique hyperfréquence) en utilisant la technologie GaAs (ED02AH) de la société OMMIC. En particulier, les circuits d'adaptation et de polarisation n'ont pas été représentés par commodité.

Le générateur de base vectorielle 1 présente un circuit diviseur une voie vers trois voies réalisé par trois amplificateurs dont l'entrée de chaque est relié à l'oscillateur local LO. En l'occurrence, chaque amplificateur est mis en œuvre sous la forme d'un transistor T1 de type FET 20µm x 4. Le fait de recourir à un circuit diviseur à base d'amplificateurs permet de maintenir un réponse constante sur une très large bande de fréquence.

Les transistors T1 sont suivis par des circuits déphaseurs respectifs pour fournir les trois signaux de sortie déphasés entre eux. En l'occurrence, il est recouru à deux filtres passe-tout et un filtre passe-bande du quatrième ordre. Les valeurs suivantes des composants fournissent un déphasage de 120° entre deux voies consécutives de sortie du générateur de base vectorielle 1 dans la bande de fréquence 1,8-5,5 GHz :

| C1a: 0,16 pF | Cb: 0,47 pF | C1c: 0,31 pF |

|--------------|-------------|--------------|

| C2a: 0,65 pF | Lb: 4,2 nH  | C2c: 1,25 pF |

| La: 2.9 nH   | Lc : 5.6 nH |              |

Les sommateurs 3a, 3b et 3c ainsi que les capteurs de puissance 4a, 4b et 4c sont réalisés de façon identique. Pour cette raison, seuls les composants du sommateur 3a et du capteur de puissance 4a sont référencés sur la figure 3.

Les sommateurs 3a, 3b et 3c sont chacun réalisés par une paire de transistor T2 montés en amplificateur différentiel. En l'occurrence, les transistors T2 sont du type

10

15

20

25

30

FET 20μm x 2. L'utilisation des transistors apporte l'avantage de fonctionner dans une bande large de fréquences en comparaison avec les sommateurs utilisant des lignes de transmission. De plus, ils offrent le choix de l'amplification, ce qui peut être un avantage lorsqu'on envisage utiliser le circuit avec des signaux RF de faible puissance. Les capteurs de puissance 4a, 4b et 4c sont chacun constitués par un transistor T3 en l'occurrence du type FET 10μm x 1 avec le canal proche du pincement, ce qui le fait opérer dans un régime très non-linéaire qui s'approche de celui d'une diode Schottky. Ils sont chacun suivis d'un filtre passe-bas pour retenir que les termes du deuxième ordre résultant de l'addition de signaux opérée par les sommateurs 3a, 3b et 3c. En l'occurrence, chaque filtre passe-bas comprend les résistances R1 et R2 et le condensateur C3 dont les valeurs sont :

R1 : 0,5 kΩ R2 : 10 kΩ C3 : 10 pF

Le filtre passe-bas de chaque capteur de puissance 4a, 4b et 4c délivre une tension de sortie respective Va, Vb et Vc qui est ensuite numérisée par le bloc de conversion analogique/numérique 5 - non représenté sur la figure 3 - aux fins de traitement numérique pour fournir les composantes cartésiennes de l'enveloppe complexe du signal modulé RFin.

Il est précisé que dans le circuit de la figure 3, le signal modulé RFin est appliqué aux grilles de trois transistors des sommateur 3a, 3, et 3c. La liaison de leurs grilles est possible du fait que l'isolation entre drain et grille est très élevée, ce qui permet de considérer le transistor comme étant unidirectionnel. Le circuit d'adaptation – non représenté - prend en compte le facteur de réflexion des trois transistors pour permettre l'adaptation. Individuellement, chaque transistor fonctionne comme un amplificateur. De la sorte est obtenu le circuit diviseur référence 2 sur la figure 2.

Les amplificateurs à gain variable 8a, 8b et 8c du modulateur M sont tous réalisés de façon identique, raison pour laquelle seuls les composants de l'amplificateur 8a sont référencés sur la figure 3. Chaque amplificateur comprend deux transistors T4 et T5 montés en cascode. Les tensions de commande de gain sont symbolisés par les générateurs 10a, 10b et 10c respectivement. En l'occurrence, les transistors T4 sont du type FET 25µm x 4 et les transistors T5 sont du type FET 22,5µm x 2. Le fait d'utiliser des amplificateurs 8a, 8b et 8c de type cascode est avantageux car il suffit de connecter ensemble leurs sorties pour réaliser l'additionneur 9 étant donné leur grand isolement.

Enfin, l'émetteur-récepteur comprend un bloc de commutation 11 qui permet sélectivement de relier ensemble ou d'isoler la sortie RFout du modulateur et l'entrée RFin du démodulateur en fonction d'un signal de commande appliqué à l'entrée 12. Cela permet de mettre en œuvre la procédure de calibration automatique du

5

10

15

20

25

30

modulateur ou du démodulateur comme décrit précédemment en référence à la figure 2. Le bloc 11 est basé sur quatre transistors T6, en l'occurrence du type FET 65μm x 8.

Les figures 4 à 6 illustrent les résultats obtenus avec le circuit décrit en référence à la figure 3.

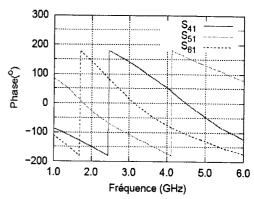

Plus particulièrement, la figure 4 montre les coefficients de transmission des trois voies du générateur de base vectorielle 1. Le module des coefficients se situe entre -7 dB et -17 dB dans la bande comprise entre 1,8 GHz et 5,5 GHz. En ce qui concerne le déphasage, nous obtenons 120° relatifs entre les trois voies aux environs de 3,5 GHz, et aux extrémités les écarts de phase sont d'environ 80° et 160°.

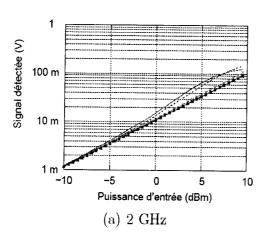

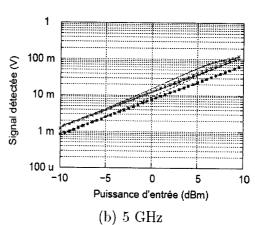

Les tensions mesurées aux sorties de détecteurs avant et après une procédure de linéarisation sont présentées sur la figure 5. Les détecteurs ne pouvant pas être caractérisés de façon isolée, nous avons appliqué une pente de puissance variant de - 10 dBm à 1'entrée du circuit démodulateur pour deux fréquences distinctes, à savoir 2 GHz et 5 GHz.

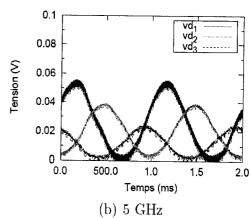

Nous avons appliqué un signal à 0 dBm à l'entrée du générateur de base vectorielle 1 et un autre signal à -3 dBm à l'entrée du démodulateur. Nous avons effectué des mesures à 2 GHz et à 5 GHz en fixant un décalage de 1 kHz entre les deux générateurs. Les tensions mesurées sont illustrées par la Fig. 6.

Ces résultats montrent que le circuit est capable de fournir des tensions en bande de base qui correspondent à la puissance du signal résultant de l'addition de deux signaux RF combinés sur différents déphasages, ce qui permet de calculer le rapport complexe entre ces deux signaux et donc d'accomplir la fonction de démodulation. De plus, il a été montré que l'amplitude de trois signaux RF déphasés est variée en fonction d'une tension de contrôle, ce qui permet de réaliser la fonction modulation.

Bien entendu, la présente invention n'est pas limitée aux exemples et au mode de réalisation décrits et représentés, mais elle est susceptible de nombreuses variantes accessibles à l'homme de l'art.

5

10

15

20

25

#### <u>REVENDICATIONS</u>

- 1. Dispositif d'addition vectorielle de deux signaux électriques 5 alternatifs modulés ou non, comprenant :

- une première entrée pour recevoir un premier signal électrique alternatif (LO);

- une deuxième entrée pour recevoir un deuxième signal électrique alternatif (RFin);

- un premier circuit (1) relié à la première entrée et comprenant un nombre n de sorties, le premier circuit fournissant, à partir du premier signal alternatif (LO) appliqué à la première entrée, un signal alternatif respectif sur chacune des n sorties, lesdits signaux alternatifs fournis sur les n sorties étant tous de même amplitude et de même fréquence mais déphasés entre eux pour que chacun soit ni en phase ni en opposition de phase avec aucun autre;

- un deuxième circuit (2) relié à la deuxième entrée (RFin) et comprenant un même nombre n de sorties, le deuxième circuit divisant le deuxième signal alternatif vers ses n sorties ; et

- un même nombre n de sommateurs (3a, 3b, 3c) recevant chacun en entrée une sortie respective du premier circuit (1) et une sortie respective du deuxième circuit (2);

dans lequel le nombre n est supérieur ou égal à 3.

- 2. Dispositif selon la revendication 1, dans lequel chacun des signaux alternatifs fournis par le premier circuit sur ses n sorties est déphasé par rapport à chacun des autres signaux alternatifs fournis par le premier circuit sur ses n sorties de 20° à 160° en avance ou en retard.

- 3. Dispositif selon la revendication 1 ou 2, dans lequel les sommateurs comprennent chacun deux transistors (T2) montés en amplificateur différentiel.

- 4. Dispositif selon l'une quelconque des revendications 1 à 3, dans lequel le premier circuit comprend un même nombre n d'amplificateurs (T1), l'entrée de chacun des amplificateurs étant reliée à la première entrée (LO) et la sortie de chacun des amplificateurs étant ensuite relié à un circuit de déphasage respectif.

- 5. Dispositif selon l'une quelconque des revendications 1 à 4, dans lequel le nombre n est égal à 3.

10

15

- 6. Dispositif selon la revendication 5, dans lequel chacun des signaux alternatifs fournis par le premier circuit sur ses trois sorties est déphasé par rapport à chacun des deux autres signaux alternatifs fournis par le premier circuit sur ses trois sorties par un angle de 80° à 160° en avance ou en retard.

- 7. Dispositif selon la revendication 6, dans lequel chacun des signaux alternatifs fournis par le premier circuit sur ses trois sorties est déphasé par rapport à chacun des deux autres signaux alternatifs fournis par le premier circuit sur ses trois sorties par un angle de 120° en avance ou en retard.

- 8. Dispositif selon l'une quelconque des revendications 1 à 7, dans lequel la sortie de chacun des sommateurs (3a, 3b, 3c) est reliée à un capteur de puissance respectif (4a, 4b, 4c).

15

20

35

10

- 9. Démodulateur par conversion directe de fréquence, comprenant :

- un dispositif d'addition vectorielle selon la revendication 8;

- un même nombre n de convertisseurs analogique/numérique (5) relié chacun à un capteur de puissance (4a, 4b, 4c) respectif; et

- un circuit de traitement numérique (6) déterminant les composantes cartésiennes de l'enveloppe complexe du signal (RFin) appliqué à la deuxième entrée du dispositif d'addition vectoriel à partir des mesures fournies par les n capteurs de puissance (4a, 4b, 4c).

- 25 10. Récepteur RF, comprenant :

- un démodulateur selon la revendication 9;

- un oscillateur local (LO) relié à la première entrée du dispositif d'addition vectorielle ;

- une antenne de réception RF; et

- our amplificateur du signal reçu par l'antenne pour l'appliquer à la deuxième entrée (RFin) du dispositif d'addition vectorielle.

- 11. Modulateur-démodulateur par conversion directe de fréquence, comprenant un démodulateur selon la revendication 9 et dans lequel le modulateur (M) comprend :

- un même nombre n d'amplificateurs à gain variable (8a, 8b, 8c), l'entrée de chaque amplificateur étant reliée à une sortie respective du premier circuit (1) du dispositif d'addition vectorielle;

- un sommateur (9) recevant en entrée la sortie de chacun des n amplificateurs à gain variable (8a, 8b, 8c);

- un circuit de traitement numérique (6) fournissant un même nombre n de commandes de gain d'amplificateur à partir des composantes cartésiennes de l'enveloppe complexe à fournir par modulation ; et

- un même nombre n de convertisseurs numériques/analogiques (7), l'entrée de chacun étant reliée au circuit de traitement numérique (6) et la sortie de chacun étant reliée à l'entrée de commande de gain d'un amplificateur respectif.

- 10 12. Modulateur-démodulateur selon la revendication 11, comprenant un circuit (20) permettant de relier sélectivement la deuxième entrée (RFin) du circuit d'addition vectorielle à la sortie (RFout) du sommateur (9) recevant en entrée la sortie de chacun des n amplificateurs à gain variable.

- 13. Emetteur-récepteur, comprenant :

5

15

20

- un modulateur-démodulateur selon la revendication 11 ou 12;

- un oscillateur local (LO) reliée à la première entrée du dispositif d'addition vectorielle ; et

- au moins une antenne RF et au moins un amplificateur pour alimenter la deuxième entrée (RFin) du dispositif d'addition vectorielle et pour émettre le signal obtenu à la sortie (RFout) du sommateur (9) relié aux n amplificateurs à gain variable.

- 14. Procédé de calibration du modulateur (M) d'un modulateurdémodulateur selon la revendication 12 à une fréquence donnée, le démodulateur (D) ayant été préalablement calibré à la fréquence donnée, le procédé comprenant les étapes de :

- application d'un signal alternatif à la fréquence donnée à la première entrée du dispositif d'addition vectorielle ;

- mise en liaison de la deuxième entrée (RFin) du circuit d'addition vectorielle à la sortie (RFout) du sommateur (9) recevant en entrée la sortie de chacun des n amplificateurs à gain variable;

- génération par le modulateur (M) de signaux modulés à partir des composantes cartésiennes d'enveloppe complexe de signaux ;

- comparaison des composantes cartésiennes d'enveloppe complexe fournis par le démodulateur (D) en conséquence de l'étape précédente avec les composantes cartésiennes d'enveloppe complexe de signaux ayant servi à la génération des signaux modulés ; et

- calibration du modulateur (M) en fonction des résultats de l'étape précédente.

- 15. Procédé de calibration du démodulateur (D) d'un modulateur-démodulateur selon la revendication 12 à une fréquence donnée, le modulateur (M) ayant été préalablement calibré à la fréquence donnée, le procédé comprenant les étapes de :

- application d'un signal alternatif à la fréquence donnée à la première entrée du dispositif d'addition vectorielle ;

- mise en liaison de la deuxième entrée (RFin) du circuit d'addition vectorielle à la sortie (RFout) du sommateur (9) recevant en entrée la sortie de chacun des n amplificateurs à gain variable;

- génération par le modulateur (M) de signaux modulés à partir des composantes cartésiennes d'enveloppe complexe de signaux ;

- comparaison des composantes cartésiennes d'enveloppe complexe fournis par le démodulateur (D) en conséquence de l'étape précédente avec les composantes cartésiennes d'enveloppe complexe de signaux ayant servi à la génération des signaux modulés; et

- calibration du démodulateur (D) en fonction des résultats de l'étape précédente.

10

3/3

Fig. 5

FIG. 4

FIG. 5

FIG. 6

### RAPPORT DE RECHERCHE PRÉLIMINAIRE

établi sur la base des dernières revendications déposées avant le commencement de la recherche

N° d'enregistrement national

FA 657145 FR 0410644

| DOC                                                                                                                                                                                                                          | JMENTS CONSIDÉRÉS COMME PE                                                                                                                                                                                                                                                                                | Revendication(s) concernée(s)                                                                                                                  | Classement attribué<br>à l'invention par l'INPI                                  |                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Catégorie                                                                                                                                                                                                                    | Citation du document avec indication, en cas de be<br>des parties pertinentes                                                                                                                                                                                                                             | esoin,                                                                                                                                         |                                                                                  | ·                                                                    |

| D,X                                                                                                                                                                                                                          | US 5 095 536 A (LOPER ET AL)<br>10 mars 1992 (1992-03-10)<br>* figures 2,3 *<br>* colonne 3, ligne 41 - colon<br>28 *                                                                                                                                                                                     | 14,15                                                                                                                                          | G06G7/22<br>H04L27/18<br>H04B1/30                                                |                                                                      |

| Υ                                                                                                                                                                                                                            | * colonne 9, ligne 7 - ligne                                                                                                                                                                                                                                                                              | 22 *                                                                                                                                           | 14,15                                                                            |                                                                      |

| D,Y                                                                                                                                                                                                                          | RANGEL DE SOUSA F ET AL: "A for automatic calibration of reflectometers" MICROWAVE AND OPTOELECTRONICS 2003. IMOC 2003. PROCEEDINGS SBMO/IEEE MTT-S INTERNATIONAL 2003, PISCATAWAY, NJ, USA, IEE vol. 2, 20 septembre 2003 (20 pages 1063-1068, XP010667609 ISBN: 0-7803-7824-5 * le document en entier * | 5-port<br>CONFERENCE,<br>OF THE 2003<br>20-23 SEPT.                                                                                            | 14,15                                                                            |                                                                      |

| A                                                                                                                                                                                                                            | EP 0 957 614 A (SONY INTERNAT 17 novembre 1999 (1999-11-17) * page 7, ligne 33 - ligne 54 1,5,7 *                                                                                                                                                                                                         | ,                                                                                                                                              | 14,15                                                                            | DOMAINES TECHNIQUES<br>RECHERCHÉS (Int.CL.7)<br>H04B<br>H03D<br>H04L |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                |                                                                                  |                                                                      |

| Date d'achèvement de la re                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                |                                                                                  |                                                                      |

| CATÉGORIE DES DOCUMENTS CITÉS  X : particulièrement pertinent à lui seul Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie A : arrière-plan technologique O : divulgation non-écrite |                                                                                                                                                                                                                                                                                                           | T : théorie ou principe<br>E : document de brev<br>à la date de dépôt<br>de dépôt ou qu'à u<br>D : cité dans la dema<br>L : cité pour d'autres | ret bénéficiant d'u<br>et qui n'a été pub<br>ne date postérier<br>nde<br>raisons | ine date antérieure<br>ilié qu'à cette date                          |

| P : doc                                                                                                                                                                                                                      | ument intercalaire                                                                                                                                                                                                                                                                                        | & : membre de la mêi                                                                                                                           |                                                                                  |                                                                      |

## ANNEXE AU RAPPORT DE RECHERCHE PRÉLIMINAIRE RELATIF A LA DEMANDE DE BREVET FRANÇAIS NO. FR 0410644 FA 657145

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche préliminaire visé ci-dessus.

Les dits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du 30-05-2005 Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets, ni de l'Administration française

| Document brevet cité<br>au rapport de recherch |   | Date de publication |                                                          | Membre(s) de la famille de brevet(s)                                                                                                                   | Date de publication                                                                                |

|------------------------------------------------|---|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| US 5095536                                     | Α | 10-03-1992          | AUCI                                                     | JN                                                                                                                                                     | <b>'</b>                                                                                           |

| EP 0957614                                     | A | 17-11-1999          | EP<br>AU<br>CA<br>CN<br>DE<br>WO<br>EP<br>JP<br>TW<br>US | 0957614 A1<br>2274899 A<br>2280870 A1<br>1252183 A<br>69825148 D1<br>69825148 T2<br>9933166 A1<br>0962047 A1<br>2002514376 T<br>493328 B<br>6650178 B1 | 17-11-1999 12-07-1999 01-07-1999 03-05-2009 26-08-2009 10-07-1999 08-12-1999 14-05-2009 01-07-2009 |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |

|                                                |   |                     |                                                          |                                                                                                                                                        |                                                                                                    |